PCB设计中的隐形艺术:Copper Thieving技术深度解析与实战指南

发布时间:2025/6/10 18:10:58

引言:当PCB设计遇上"铜块盗窃案"

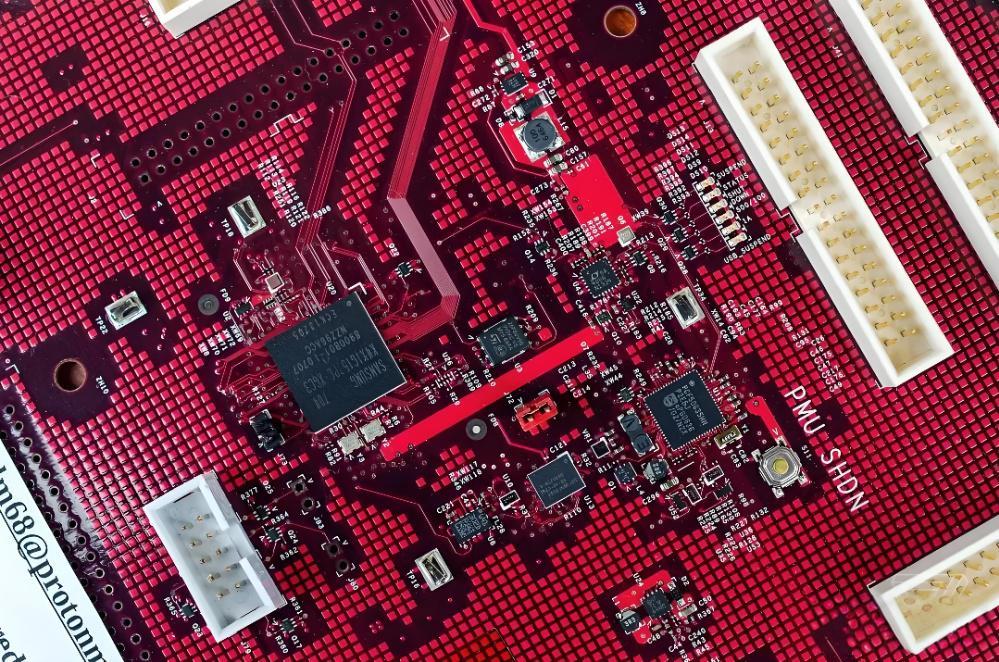

在电子制造领域,PCB设计堪称现代电子产品的基因蓝图。当我们拆解iPhone原型机时,那些看似装饰性的棋盘格铜块背后,竟隐藏着影响电路性能的关键技术——Copper Thieving(铜盗取技术)。这项被工程师戏称为"在PCB上盗铜"的工艺,实则是保障高速数字电路稳定运行的隐形守护者。本文将带您深入解析这项融合了电磁学、材料学与制造工艺的精密技术,揭示其如何平衡电镀电流、优化信号完整性,并最终决定着消费电子产品的性能边界。

一、Copper Thieving技术本质解析

1.1 定义与工作原理

Copper Thieving,中文译作铜盗取技术或均流块,本质是在PCB外层特定区域布置非功能性铜块矩阵。这些独立铜块既不参与电路连接,也不构成天线结构,其核心价值体现在电镀工艺阶段:通过调节电流密度分布,实现全板铜厚度的精准控制。

电镀电流平衡公式:

J=AI=k⋅ρ

(J为电流密度,I为总电流,A为有效电镀面积,ρ为铜箔电阻率,k为工艺常数)

当BGA封装区等高密度走线区域(A₁)与空闲区域(A₂)的铜箔面积差异过大时,电流密度比值:

J2J1=ρ2ρ1⋅A1A2

会导致铜厚差异超过±10%的行业标准,引发信号完整性灾难。

1.2 视觉特征与分类

典型Copper Thieving呈现两种几何形态:

- 棋盘格矩阵:边长0.5-2.0mm的正方形铜块,间距0.2-0.5mm

- 蜂窝状阵列:直径0.3-1.5mm的圆形铜点,采用六边形密堆积布局

这些微型结构的物理尺寸(λ/4,λ为工作波长)远小于电磁辐射临界值,从源头杜绝了意外天线的产生。

二、电磁兼容性(EMC)设计中的双刃剑效应

2.1 传统覆铜的EMC困境

在高速数字电路中,外层完整覆铜层可能引发:

-

Patch天线效应:未打孔的铜箔区域等效为微带天线,辐射效率公式:

η=λ24π2A⋅Q(A为有效辐射面积,Q为品质因数)

-

谐振风险:当铜箔尺寸接近λ/2整数倍时,输入阻抗:

Zin=2Z0⋅sin(βl)cos(βl)(β为相位常数,l为传输线长度)

2.2 智能覆铜策略

对于高速数字电路(>1GHz),推荐分层策略:

| 层数 | 推荐处理方式 | 关键参数 |

|---|---|---|

| 顶层 | 局部覆铜(<30%面积) | 铜块间距>0.5mm |

| 内层1 | 完整参考平面 | 介质厚度<4mil |

| 内层2 | 带状线隔离带 | 隔离带宽>20mil |

| 底层 | 器件散热区局部覆铜 | 铜箔厚度>1oz |

三、制造工艺与信号完整性的博弈

3.1 电镀工艺优化

UG等现代PCB厂家采用动态脉冲电镀技术,通过调节脉冲占空比(D)实现:

- 脉冲频率:500-2000Hz

- 峰值电流密度:3-5ASD

- 反向脉冲时间:10-20%周期

3.2 阻抗控制关键点

在50Ω微带线设计中,Copper Thieving的引入会导致:

-

特征阻抗变化量:

ΔZ0=2Z0⋅WΔW(W为线宽,ΔW为有效线宽变化)

-

损耗正切角增量:

Δtanδ=2hd⋅ϵr0.5

(d为铜块间距,h为介质厚度)

要求Copper Thieving区域与控制阻抗线保持至少3倍线宽的安全距离。

四、EDA工具赋能设计革新

4.1 主流工具功能对比

| 工具名称 | Copper Thieving功能 | 特色优势 |

|---|---|---|

| Cadence Allegro | 智能填充引擎+DRC校验 | 与SI/PI仿真无缝集成 |

| Mentor PADS | 自动残铜率分析+3D可视化 | 支持异形铜块生成 |

| Altium Designer | 规则驱动填充+批量修改 | 集成MCAD协作模块 |

4.2 最佳实践流程

- 前期规划:在Stackup设计时预留Thieving专用层

-

参数设置:

- 铜块尺寸:0.5-1.0mm(根据制造精度调整)

- 间距规则:最小0.15mm(满足DFM要求)

- 区域排除:避开关键信号线±50mil范围

-

验证阶段:

- 电流密度仿真(推荐使用ANSYS SIwave)

- 热应力分析(确保压合均匀性)

五、实战案例:iPhone原型板技术解密

5.1 历史版本演进

初代iPhone开发板(2006年)的Copper Thieving设计呈现三大特征:

- 棋盘格密度梯度:BGA区域密度达60%,边缘区域降至20%

- 动态间距调整:靠近USB接口区域采用0.2mm间距

- 热应力补偿:在压合敏感区嵌入0.5mm铜块阵列

5.2 现代演进趋势

当前智能手机主板设计的新趋势:

- AI加速区域:采用自适应密度填充(ADF)技术

- 5G毫米波区域:集成频率选择表面(FSS)结构

- 散热优化区:开发相变材料填充的铜块矩阵

六、PCB设计规范与制造协同

6.1 DFM检查清单

- 铜块与最近过孔间距>0.25mm

- 残铜率控制在40%-60%区间

- 压合平衡度:内层铜分布差异<15%

- 耐化学腐蚀测试:满足IPC-TM-650 2.6.15标准

6.2 供应商沟通要点

需向PCB厂商提供:

- Thieving区域Gerber文件(单独层)

- 电流密度分布热力图

- 压合模拟报告(含树脂流动预测)

结论:重新定义PCB设计美学

Copper Thieving技术完美诠释了现代电子设计的哲学:在微观尺度上重构材料分布,用几何美学平衡物理规律。从初代iPhone的探索性尝试,到当前5G终端的精密设计,这项技术持续推动着PCB设计的边界。对于工程师而言,掌握这项"盗铜艺术",意味着在信号完整性、可制造性与成本控制的三角关系中,找到了新的平衡支点。