高速PCB布线的艺术

发布时间:2025/2/25 14:34:37

在当今的电子产品设计中,嵌入式芯片的主频越来越高,高速电路已成为许多设备的核心组成部分。与低速电路不同,高速电路的PCB布线不仅需要遵循基本的布线规则,还需特别关注信号完整性(SI)和电源完整性(PI)问题。一旦忽视这些关键点,信号失真、串扰、反射等问题将直接影响系统性能,甚至导致产品失效。本文将深入探讨高速PCB布线的核心注意事项,结合专业公式与设计实践,为PCB设计工程师们提供一套系统化的解决方案。

一、阻抗控制:高速信号的“生命线”

阻抗控制是高速PCB设计的基石。信号在传输过程中,阻抗不匹配会导致信号反射,进而引发信号完整性问题。因此,设计时必须精确控制走线阻抗。

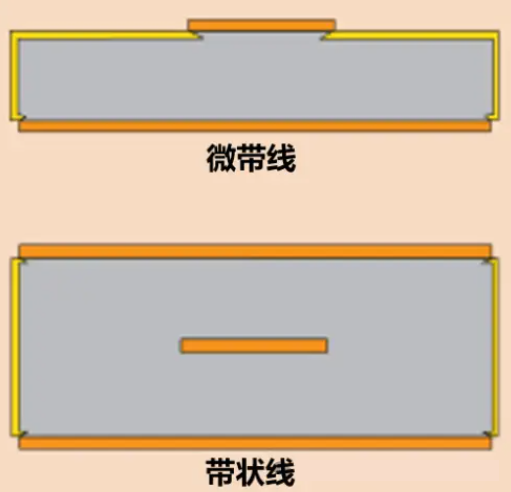

1. 传输线结构的选择

根据信号频率、板厚、介电常数等因素,选择合适的传输线结构至关重要。常见的传输线结构包括微带线(Microstrip)和带状线(Stripline)。微带线适用于表层布线,而带状线则适用于内层布线,具有更好的抗干扰能力。

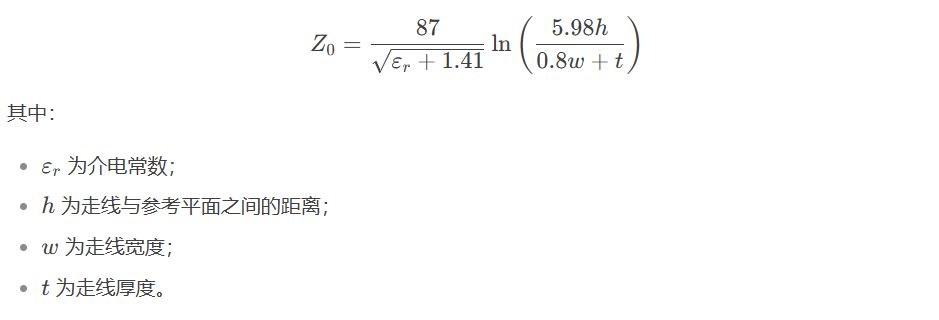

2. 阻抗计算与匹配

阻抗的计算是高速PCB设计的关键步骤。以微带线为例,其特性阻抗 Z0可以通过以下公式计算:

通过阻抗计算工具(如Polar SI9000),工程师可以精确设计走线宽度和间距。例如,对于90欧姆的差分线阻抗,走线宽度和间距需严格符合计算结果。

3. 避免阻抗不连续

阻抗不连续是信号反射的主要来源。设计中应避免走线出现直角拐弯、过孔、分支或线宽变化。对于必须使用的过孔,可采用背钻技术(Back Drilling)或优化过孔设计,以减少寄生电容和电感的影响。

二、减少串扰:高速信号的“隐形杀手”

串扰是高速PCB设计中的另一大挑战。当两条走线距离过近时,电磁耦合会导致信号相互干扰,从而影响信号质量。

1. 3W规则

为减少串扰,相邻走线之间的间距应遵循3W规则,即走线间距至少为走线宽度的3倍。例如,若走线宽度为6mil,则间距应至少为18mil。

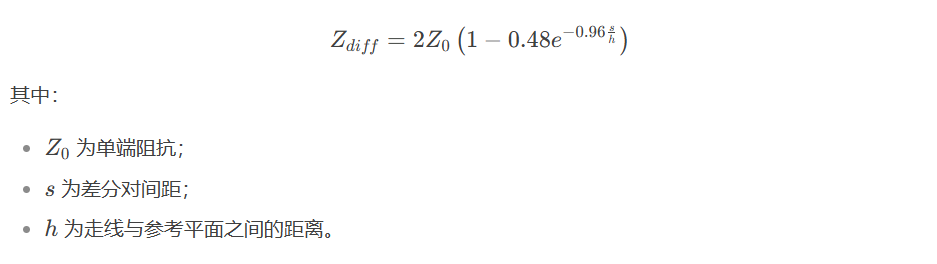

2. 差分信号的使用

差分信号是抑制共模噪声的有效手段。差分对的走线需严格等长,且阻抗需匹配。差分阻抗的计算公式如下:

3. 屏蔽与隔离

在敏感信号周围添加地平面(GND)作为屏蔽层,可以有效隔离外界干扰。此外,尽量避免长距离平行走线,以减少电磁耦合。

三、避免反射:信号的“回音壁”

信号反射会导致波形失真,严重时甚至引发逻辑错误。为避免反射,需从走线长度和端接方式两方面入手。

1. 控制走线长度

走线长度应尽量短,以减少信号传输延迟和反射。对于关键信号,走线长度需严格控制在允许范围内。

2. 端接电阻的使用

在信号终端添加端接电阻,可以匹配阻抗,避免信号反射。常见的端接方式包括串联端接和并联端接。串联端接适用于驱动端,而并联端接适用于接收端。

四、优化电源与地:系统的“能量之源”

电源和地平面的设计直接影响系统的稳定性和噪声性能。

1. 低阻抗电源平面

采用完整的电源和地平面,可以降低电源阻抗,提供稳定的电源供应。电源平面的设计需避免分割,以确保回流路径畅通。

2. 去耦电容的布置

在电源引脚附近合理布置去耦电容,可以滤除高频噪声,保证电源完整性。去耦电容的容值选择需根据信号频率和电源噪声特性进行优化。

五、其他关键注意事项

1. 过孔优化

过孔会引入寄生电感和电容,影响信号完整性。设计中应尽量减少过孔数量,并采用盲孔、埋孔等技术优化过孔设计。

2. 散热设计

高速信号会产生热量,需通过合理的散热设计(如增加散热孔或使用散热片)来避免过热问题。

3. 仿真分析

利用仿真工具(如HyperLynx或ADS)对布线方案进行仿真分析,可以验证信号完整性和电源完整性,并优化设计方案。

六、总结

高速PCB设计是一门综合性的艺术,需要工程师在阻抗控制、串扰抑制、反射避免、电源优化等方面进行全方位考量。通过精确的阻抗计算、合理的布线策略以及严格的仿真验证,才能确保信号完整性和系统性能。在实际设计中,工程师还需根据具体应用场景灵活调整方案,以实现最优的设计效果。