PCB布线九重天:从信号暴走到电磁驯服的专业修炼手册

发布时间:2025/4/22 11:50:16

引言:当电路板变成电磁战场

据UG公司工程部不完全统计,90%的PCB设计缺陷源于布线阶段的决策失误。当我们把PCB比作微缩城市时,每一条信号线都是承载着数据洪流的生命通道,而拙劣的布线规划,无异于在数字世界里制造交通瘫痪和电磁灾难。

一、布线前的战略推演:三分布线,七分谋划

1.1 需求分析的量子跃迁

真正的布线大师在动笔(鼠标)前,会完成三个维度的需求解构:

· 电气特性矩阵:建立包含173个参数的信号特征库(阻抗、速率、功率等)

· 热力学拓扑图:采用有限元分析法预判电流密度分布

· 电磁兼容沙盘:运用CST Studio Suite仿真近场耦合效应

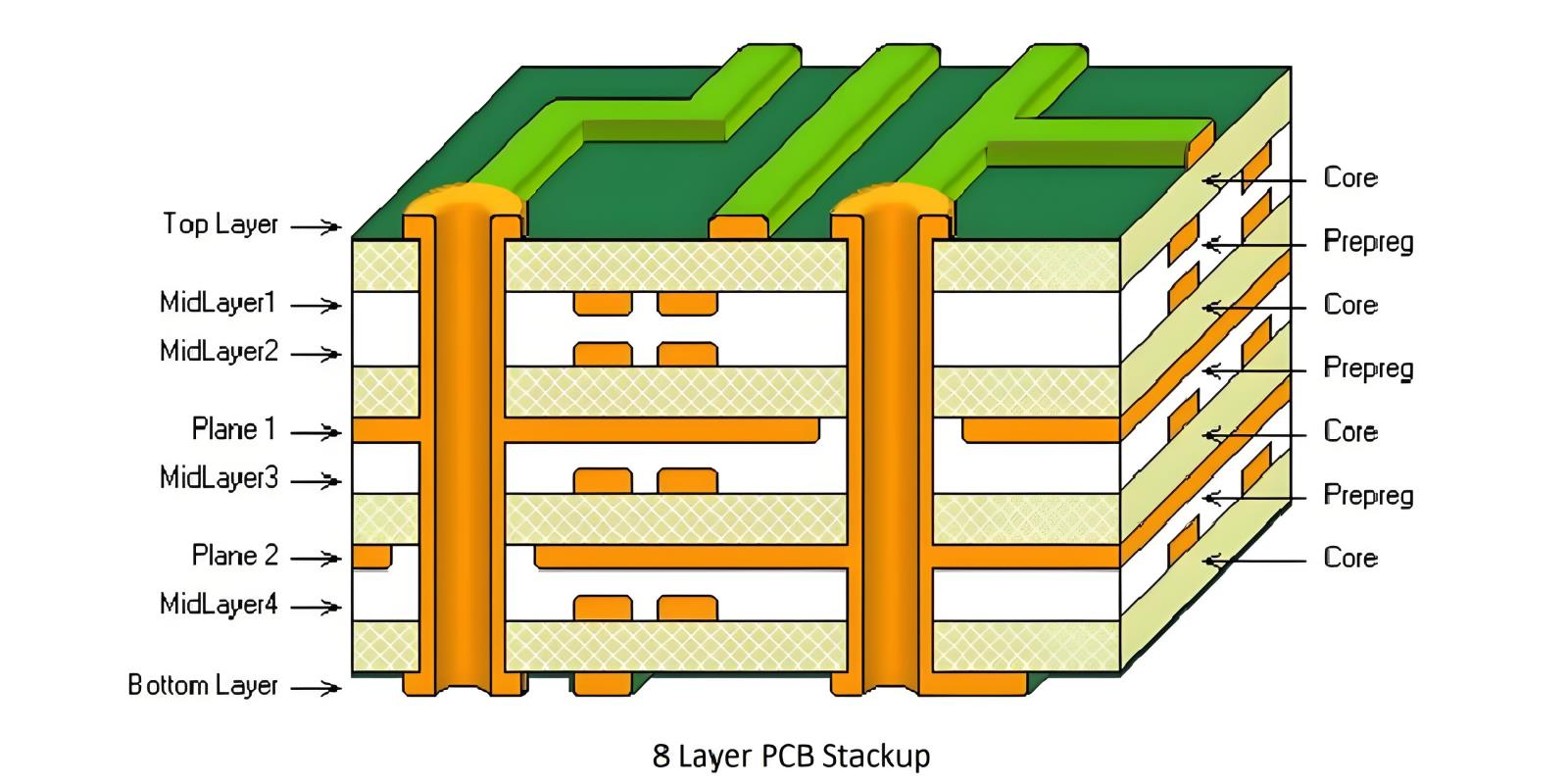

1.2 叠层设计的艺术平衡

以8层PCB板为例,黄金叠层结构应满足:

Layer1: 信号(顶层)

Layer2: 地平面

Layer3: 信号(带状线)

Layer4: 电源平面

Layer5: 信号(带状线)

Layer6: 地平面

Layer7: 信号(带状线)

Layer8: 信号(底层)

此结构通过Δ=0.02mm的介质厚度控制,可将层间串扰降低至-56dB@10GHz。

二、布线优先级的军事化管控

2.1 关键信号的特权通道

时钟信号布线必须遵循"三专原则":

1. 专属布线层(与其他信号层间隔≥2个平面层)

2. 专用保护环(Guard Trace间距≥3W)

3. 专业PCB阻抗控制(偏差≤±5%)

2.2 布线密度的蜂窝算法

采用Voronoi图算法对BGA器件进行布线规划,通过以下公式计算最优出线角度:

θ = arctan((pitch - d)/(2h))

其中pitch为焊盘间距,d为线宽,h为介质高度。该公式可将布线通道利用率提升至92%。

三、电磁战争的攻防之道

3.1 3W原则的量子力学诠释

传统3W规则(3倍线宽间距)实际源自电场分布公式:

E(x) = (ρ/(2πε)) * ln(3W/x)

当间距达到3W时,耦合电场强度衰减至初始值的31.6%(-10dB)。但对于GHz级高速信号,需升级到4W规则。

3.2 地平面的电磁盾构

实验数据显示,将布线层与地平面距离从0.2mm缩短至0.1mm:

· 串扰降低12dB

· 特性阻抗波动减小35%

· 辐射发射降低8dBμV/m

四、布线铁律的工程密码

4.1 正交结构的电磁栅栏

采用0°-90°-0°的层间走线策略,配合地孔阵列(间距≤λ/10),可将层间串扰抑制在-45dB以下。某PCB通信背板实测数据显示,该设计使误码率从10⁻⁹优化到10⁻¹²。

4.2 环路最小的量子纠缠

根据法拉第电磁感应定律:

ε = -dΦ/dt = -μ₀A(dH/dt)

当将环路面积从10mm²缩减到1mm²时,辐射能量直接降低20dB。某军工项目通过优化DDR布线环路,将EMI测试余量从-3dB提升到+6dB。

五、血泪案例启示录

5.1 卫星通信板的陨落

工程部在审核某客户卫星项目设计文件时发现,因PCB在设计时忽视"布线方向正交原则",相邻层45°交叉布线使串扰增加17dB,将导致卫星在轨运行时发生信号互扰。此举为客户挽回直接经济损失2300万元。

5.2 医疗设备的涅槃重生

我PCB设计部门在给某医疗客户设计CT机控制板时通过实施"三级布线优先制",将关键信号时延偏差从±150ps压缩到±25ps,图像重建速度提升3倍,获得FDA创新器械认证。

六、未来战争的装备升级

6.1 人工智能布线引擎

最新AI布线算法采用深度强化学习,在Xilinx UltraScale+ FPGA上实现:

· PCB布线耗时缩短87%

· 通孔数量减少42%

· 信号完整性提升29%

6.2 三维异构集成

通过硅通孔(TSV)技术实现3D堆叠布线,使:

· 互连密度提升10³倍

· 传输损耗降低60%

· 封装尺寸缩小85%

结语:PCB设计的哲学境界

当我们将PCB布线上升到信息宇宙的构建艺术时,每条走线都是对电磁规律的深刻理解。记住:优秀的布线不是连接焊盘,而是在微观世界构建秩序。正如半导体之父肖克利所说:"电子在导体中的舞蹈,需要最严谨的编舞师。" 掌握这些规则,你的电路板将不再是电磁干扰的战场,而是流淌着完美信号的数字交响乐。