一网打尽!PCB设计的终极检查清单:从信号完整性到成功量产

发布时间:2025/12/23 14:31:02

在当今从5G通信、人工智能到新能源汽车的电子浪潮中,印制电路板(PCB)已不仅仅是元器件的承载体,更是决定产品性能、可靠性与上市速度的核心。一份详尽且专业的PCB设计检查清单,是连接创新设计与成功量产之间不可或缺的桥梁。本文将从行业专家视角,深度解析PCB设计全流程中的关键检查项,助您打造高性能、高可靠性的硬件基石。

第一阶段:设计启航——规划与规则建立

成功的PCB设计始于详尽的规划与精准的规则设定。此阶段的疏忽将在后续引发连锁问题。

-

封装与库管理:这是所有物理设计的基础。务必确认原理图符号、PCB封装与实际元器件三者的引脚顺序与物理尺寸完全一致。对于结构件(如连接器)和任何新器件,必须进行三维核对,以避免昂贵的返工。

-

叠层与阻抗设计:根据电路复杂度、成本与性能需求确定层数后,阻抗控制是高速设计的生命线。应优先使用PCB制造商提供的工具(如嘉立创阻抗计算神器)或行业标准软件Polar Si9000进行仿真。影响阻抗的关键参数包括:介电常数(Er)、介质厚度(H1)、线宽(W)和铜厚(T)。例如,对于常见的FR-4材料,介电常数增加10%,微带线阻抗可能下降约6.1Ω。必须将最终确定的各阻抗线(如单端50Ω,差分100Ω)的线宽、线距规则添加到设计约束中。

-

结构协同:与结构工程师确认板框、限高区、禁布区以及所有定位孔(区分金属化与非金属化)。天线净空区必须由天线工程师明确指定并最终确认,例如2.4GHz PCB天线通常需要半径≥30mm的绝对净空区域。

第二阶段:核心实施——PCB布局与布线策略

布局布线是将电气原理转化为物理现实的艺术,需要平衡电气性能、热管理和可制造性。

-

关键器件布局:

-

精细化布线:

-

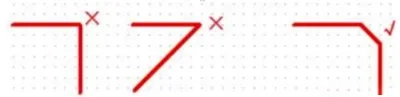

基础法则:杜绝直角走线,优先采用45°角或弧线;走线从焊盘中心引出,宽度不大于焊盘宽度;敏感线(时钟、模拟音频)与强干扰源(大电流、高速线)充分隔离。

-

高速布线黄金法则:

-

-

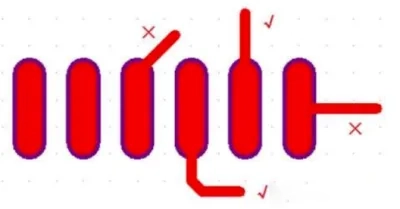

电源与接地:

第三阶段:专项优化——EMC与信号完整性

-

EMC主动设计:EMC问题必须从设计源头抑制。除了良好的接地,还需:在板边规则放置接地过孔以抑制边缘辐射;为高速连接器使用屏蔽壳体并提供360°良好接地;在接口处可选配共模扼流圈,以滤除电缆上的共模噪声。

-

信号完整性(SI)预验证:对于关键高速网络(如PCIe、高速SerDes),在投板前应使用Sigrity、HyperLynx等工具进行阻抗连续性检查和串扰仿真。这可以提前发现因跨分割、参考平面不连续或线间距不足导致的潜在问题。

第四阶段:投产冲刺——PCB设计验证与文件输出

这是将设计数据无误传递至制造工厂的最后关卡。

-

最终设计规则检查(DRC):运行全面的DRC,确保无一疏漏。

-

Gerber与生产文件生成:

-

可制造性(DFM)与可装配性(DFA)检查:

-

与制造商确认其工艺能力(最小线宽/线距、最小孔径等)是否与设计匹配。

-

提供清晰的装配图、位号图和钢网文件。与SMT贴片工厂确认拼版方案(如V-Cut、邮票孔)的合理性,确保便于分板和组装。

-

结论

在价值超过600亿美元、技术飞速迭代的中国PCB市场中,从规模扩张迈向价值跃迁的核心,正是对设计品质的极致追求。一份超越基础的、深入信号完整性、电源完整性和EMC领域的专业检查清单,是工程师将复杂高密度互联(HDI)设计、高频高速设计成功转化为稳定可靠产品的关键。它不仅能规避设计反复与成本浪费,更能显著提升产品在激烈市场竞争中的成功率。对于寻求高性能PCB设计服务或高端PCBA快速打样的团队而言,与拥有深度设计评审能力和丰富量产经验的合作伙伴共事,无疑是通往成功的最短路径。